# **Exploring the use of a NEMS Relay as an Integrated Selector Device for ReRAM**

Gina C. Adam<sup>1</sup>, Alexandru Solot<sup>2</sup>, Adrian Dinescu<sup>1</sup>, Montserrat Fernandez-Bolaños<sup>3</sup>, Adrian M. Ionescu<sup>3</sup>, Alexandru Müller<sup>1</sup>

gina.adam@imt.ro

**Abstract.** This paper proposes the use of two-terminal NEMS relays as high nonlinearity selector devices in emerging analog ReRAM crossbars useful in memory, stateful logic and neuromorphic applications. Finite element simulations were used to investigate the constraint space needed for the design of a NEMS relay with a <1V actuation voltage, as needed for compatibility with the ReRAM devices. These simulations informed the geometries explored in the fabrication of such monolithically integrated ReRAM/ NEMS hybrid devices. Preliminary experimental results are shown to describe the proposed fabrication flow based on  $SiO_2$  as an inorganic sacrificial layer for clean release and a mix of photolithography and ebeam lithography, lift-off and dry etching. These devices will be electrically tested and in future iterations, hybrid crossbars will be fabricated and tested for the correct functionality.

#### 1. Introduction

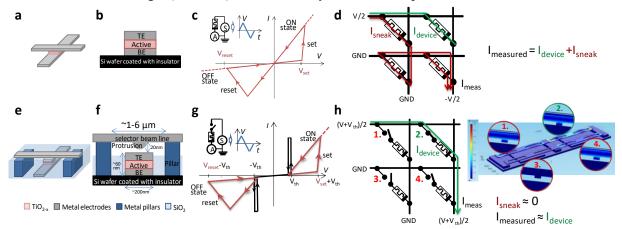

The high nonlinearity of nanoelectromechanical switches (NEMS) make them attractive as selectors for non-volatile analog crossbar memories. Two-terminal non-volatile analog memory devices, such as the resistive switches (or ReRAM or memristors), packed in a crossbar architecture, promise to deliver the high density and connectivity required for hardware implemented artificial neuronal networks (ANNs) [1-2]. However, the crossbar architecture suffers intrinsically from the sneak path problem – neighboring devices create electrical shorts around the selected device (Fig. 1a-d). Biological neuronal systems do not have this problem due to the nonlinear mechanism of their potentiation and spiking.

A solution is the use of a highly nonlinear selector device for each memory device. Despite the limited scalability and stackability, conservative configurations using a transistor [5-8] or diodes [9] as selectors have been used in a variety of novel non-volatile memory systems. Extensive effort has been spent in the field on researching material systems and device structures, such as a-Si/Ag electrodes [10], NbO<sub>x</sub> films [11], that exhibit dual diode-like selector and resistive switching behaviors, but satisfactory operation and reproducibility are hard to achieve. An interesting solution has been complementary resistive switches [12], although it has the disadvantage of a destructive readout.

This paper proposes the use of a NEMS relay as a selector, which offers several advantages: high

<sup>&</sup>lt;sup>1</sup> National Institute for R&D in Microtechnologies (IMT), Bucharest, Romania

<sup>&</sup>lt;sup>2</sup> University Politehnica of Bucharest (UPB), Bucharest, Romania

<sup>&</sup>lt;sup>3</sup> École Polytechnique Fédérale de Lausanne (EPFL), Lausanne, Switzerland

non-linearity (Fig. 1a-d vs. 1e-h), easy tunability of threshold voltage via geometry changes, ambipolar operation and potential to introduce a high contact resistance to serve as a current limiter. An ANN is typically used repeatedly for classification of the same tasks, therefore the devices are switched intensively only during initial training. A NEMS life time of  $>10^6$  cycles should suffice. Since high density is of utmost importance for hardware implemented neuronal networks, a two terminal design and sub- $\mu$ m relays should be used to allow for easy integration with the two-terminal memory devices (Fig. 1a-b and e-f). The typical size for MEMS switches is  $\sim 100 \mu$ m, but recent work [3] has shown a scalable two-terminal nanoelectromechanical (NEMS) switch with low actuation voltage ( $V_{th}<1V$ ). The pipe clip structure is based on side edge actuation and is prone to reliability issues due to stiction since the electrode width is quite large ( $\sim 300$ nm). We propose a structure based on a protrusion (dimple) small contact area and tunable dimensions during the fabrication process.

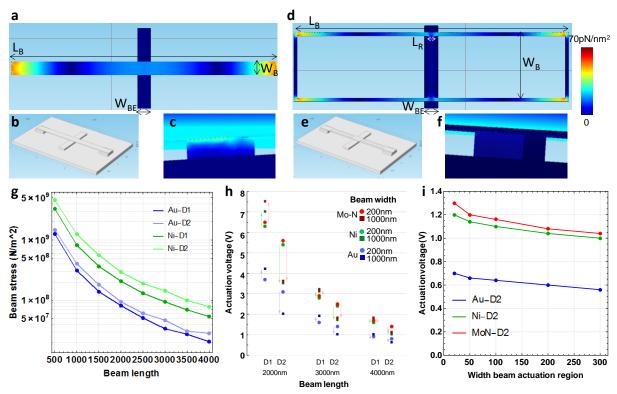

A finite element analysis using COMSOL 5.2 was done to explore the constraint space needed for the design of a NEMS relay with a <1V actuation voltage. These simulation results informed the fabrication of such integrated switches. The surface micromachining process has been developed to have a low-thermal budget ( $<450\,^{\circ}\text{C}$ ) and be multilayer CMOS compatible.

**Figure 1.** Comparison between current **ReRAM design** (a-d) and proposed **ReRAM/NEMS design** (e-h) (a) ReRAM 3D sketch (b) Cross-sectional view; and (c) I-V characteristic with almost linear ON state prone to (d) current leakages in crossbars without selectors; (e) integrated ReRAM/ NEMS selector 3D view and (f) cross-section showing two-terminal design. (f) desired I-V characteristic with nonlinearity introduced by the selector, which (h) solves the sneak path problem. The half-biased devices are only partially actuated (COMSOL) and have almost zero leakage current through them.

## 2. Device Simulation

The proposed design is based on a fixed ReRAM with a bottom electrode lines (Pt) and active layer (TiO<sub>2-x</sub>) and top electrode pads (Pt). The top electrode is shared between the memristor and the NEMS relay. The NEMS relay has a beam line supported by pillars and a small air gap. A protrusion (dimple) positioned in the center of the beam line is included to create a small contact point with the memristor electrode, used to prevent stiction problems caused by repeated actuation [4]. The structure is electrostatically actuated through a voltage applied on the beam and the fixed electrode grounded.

The geometric dimensions of the beam line and its material and airgap heights are constraints for the proposed design (Fig. 2). Two geometries of the beam – one solid and one with large gaps - were investigated. The second one showed slightly higher stress at the corners but reduced the actuation voltage by ~30%, however beam lengths of at least  $3\mu m$  are needed for a <1V actuation voltage. The material of the NEMS beam should have a small Young modulus and a high tolerance to stresses. Au is desirable since it has a small Young modulus, but it is soft and prone to stiction so Ni and the amorphous metal Mo-N were also simulated with good results. The protrusion was approximated as a cuboid of height 10nm and widths 20nm and with a gap between it and the top electrode of 5 or 10nm.

**Figure 2. Simulation results** (a-f) Von Misses stress comparison in design 1 (a-c) vs. design 2 (d-f). The beam stress and the actuation voltage decrease with the beam length (g and h). Design 2 has lower actuation voltage (g), especially if the central region is wide enough (i), but higher stress (g).

#### 3. Device Fabrication

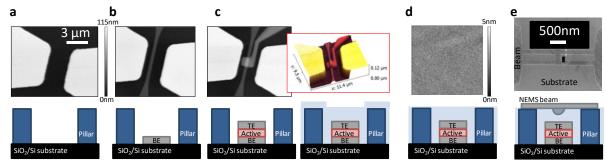

Monolithically integrated ReRAM/NEMS individual switches were fabricated on a Si wafer with 200nm thermal  $SiO_2$  for isolation. Metal pillars of various thicknesses (80nm to 100nm) and gaps between them (1µm to 6µm) were patterned using photolithography to support the NEMS beam line (Fig. 3a). The pillar thickness controls the air gap in the final structure and the pillar gap width controls the NEMS line length, these parameters being important in reducing the actuation voltage. In the gaps between the pillars, ReRAM devices were patterned (Fig. 3b,c) with dimensions between 400nm to 1.4µm. E-beam lithography can pattern small dimensions with a small alignment error, which was necessary given the small space between the pillars. A 25nm thick  $TiO_{2-x}$  film deposited with e-beam deposition from  $TiO_2$  pellets in vacuum led to a sub-stoichiometric material suitable for low voltage ReRAM devices. These structures were covered with a 500nm of PECVD  $SiO_2$ , used as sacrificial layer for the chemical mechanical planarization and temporary support of the NEMS beam (Fig. 3d). After planarization, the NEMS beam was patterned with e-beam lithography and dry etching (Fig. 3e). Several materials can be used for the beam, such as metal (Au or Ni) but also 2D materials like graphene. In future tests, a protrusion will be patterned with e-beam lithography and dry etching before the NEMS beam patterning. Finally, the sacrificial  $SiO_2$  will be removed using dry etching.

#### 4. Conclusion

In summary, this paper proposes a two-terminal sub-1V NEMS selector monolithically integrated with a ReRAM device. The simulation shows that fairly long beams ( $>3~\mu m$ ) are needed to obtain the targeted actuation voltage, which poses problems from the point of view of high density. However, the integration device has one direction that is still highly scalable and the ultra high nonlinearity could potentially outweigh the negatives for very large crossbars. Preliminary experimental results describe

the chosen fabrication flow. These devices will be electrically tested and improved in future iterations, with the goal of integrating them into crossbars and implementing a simple ANN for pattern matching.

**Figure 4. Preliminary experimental results** (a) Lift-off of e-beam deposited NEMS metal pillars (Ti 5nm/Au 95nm) of various gap widths (1 $\mu$ m to 6 $\mu$ m); (b) Lift-off of e-beam deposited bottom electrode (BE – Cr 5nm/Au 10nm/Pt 5nm) of various widths; (c) Completed memristor device with active layer (25nm e-beam deposited TiO<sub>2-x</sub>) and top electrode (TE – Pt 5nm/Au 15nm/Cr 5nm) connected for separate access for testing; (d) Planarized surface using chemical mechanical polishing (CMP); (e) E-beam lithography of the NEMS beam. With and without protrusion configurations will be tested.

# Acknowledgements

The authors thank the European Union's Horizon 2020 programme for the Marie Sklodowska-Curie grant No. 705957, and the Executive Agency for Higher Education, Research, Development and Innovation Funding (UEFISCDI) for grant no. PN-III-P3-3.6-H2020-2016-0026.

## References

- [1] S. H. Jo, T. Chang, I. Ebong, B.B. Bhadviya, P. Mazumder and W. Lu," Nanoscale memristor device as synapse in neuromorphic systems", *Nano letters*, 10(4), pp. 1297-1301, 2010.

- [2] M. Prezioso et al, "Training and operation of an integrated neuromorphic network based on metal-oxide memristors", *Nature*, 521(7550), 2015.

- [3] J.O. Lee, Y.H. Song, M.W. Kim, M.H. Kang, J.S. Oh, H.H Yang, and J.B. Yoon, "A sub-1-volt nanoelectromechanical switching device", *Nature nanotechnology*, 8(1), 36-40, 2013.

- [4] G.M. Rebeiz, RF MEMS: theory, design, and technology, John Wiley & Sons, 2004.

- [5] H. Chung et al. "A 58nm 1.8 v 1gb pram with 6.4 mb/s program bw." *Proc. of Solid-State Circuits Conference (ISSCC)*, pp. 500-502, 2011.

- [6] R. Nebashi et al. "A 90nm 12ns 32Mb 2T1MTJ MRAM." *Proc. of Solid-State Circuits Conference (ISSCC)*, pp. 462-463, 2009.

- [7] S.S. Sheu et al. "A 5ns fast write multi-level non-volatile 1 K bits RRAM memory with advance write scheme." *Symposium of VLSI Circuits*, pp. 82-83, 2009.

- [8] M. Qazi, M. Clinton, S. Bartling, A.P. Chandrakasan "A low-voltage 1Mb FeRAM in 0.13 μm CMOS featuring time-to-digital sensing for expanded operating margin in scaled CMOS", *Proc. of Solid-State Circuits Conference (ISSCC)*, pp. 208-210, 2011.

- [9] D. Golubović et al. "Vertical poly-Si select PN-diodes for emerging resistive non-volatile memories." *Microelectronic Engineering* 84, no. 12, pp. 2921-2926, 2007.

- [10] K. H. Kim, S. Hyun Jo, S. Gaba, W. Lu, "Nanoscale resistive memory with intrinsic diode characteristics and long endurance", *Applied Physics Letters*, 96(5), 053106, 2010.

- [11] J. Bae et al. "Coexistence of bi-stable memory and mono-stable threshold resistance switching phenomena in amorphous NbOx films" *Applied Physics Letters*, 100(6), 062902, 2012.

- [12] E. Linn, R. Rosezin, C. Kügeler, R. Waser "Complementary resistive switches for passive nanocrossbar memories" *Nature materials*, 9(5), 403-406, 2010.